- 您现在的位置:买卖IC网 > Sheet目录1236 > PCI-EXP-T42G5-N1 (Lattice Semiconductor Corporation)IP CORE PCI EXPRESS ORCA 4

�� �

�

Lattice� Semiconductor�

�PCI� Express� User’s� Guide�

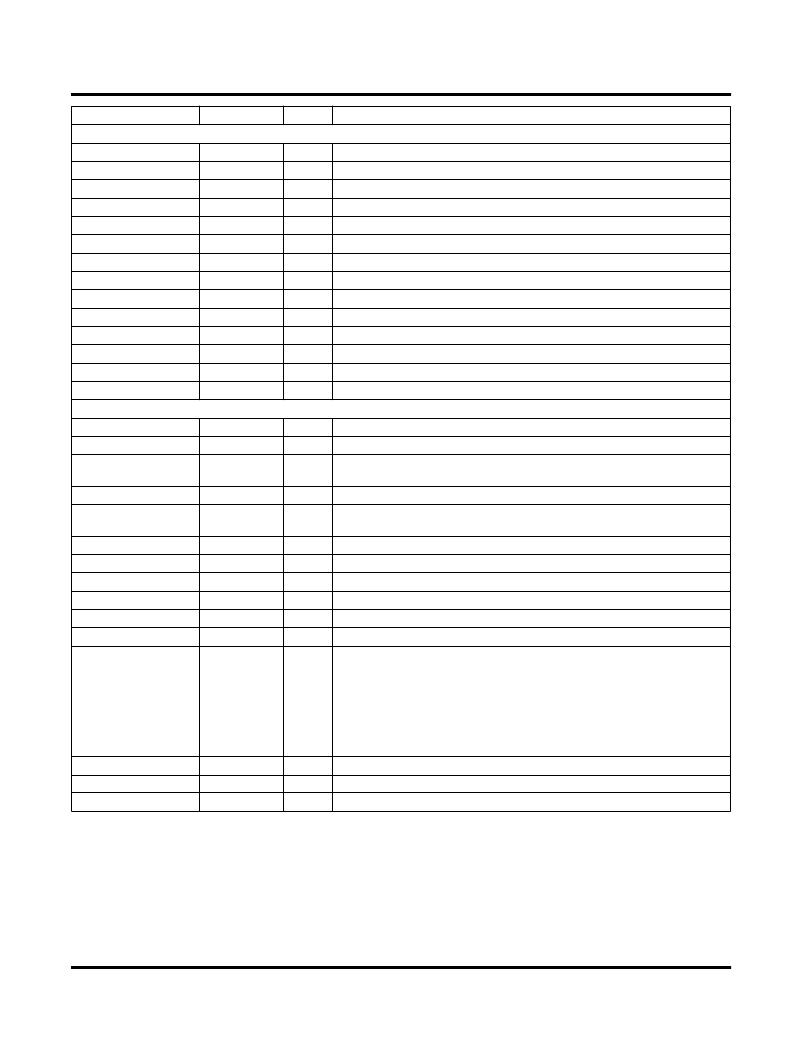

�Port� Name�

�Active� State�

�I/O�

�Signal� Description�

�RX_USR� Interface�

�rxtlpu_data[31:0]�

�rxtlpu_st�

�rxtlpu_sd�

�rxtlpu_end�

�rxpm_dllp_type�

�rxpm_dllp_val�

�pois_tlp�

�un_sup_req�

�malf_tlp�

�bad_tlp�

�bad_dllp�

�dll_perr�

�rnum_rlor�

�rply_tout�

�—�

�High�

�High�

�High�

�—�

�High�

�High�

�High�

�High�

�High�

�High�

�High�

�High�

�High�

�O�

�O�

�O�

�O�

�O�

�O�

�O�

�O�

�O�

�O�

�O�

�O�

�O�

�O�

�Received� TLP� Data� to� Transaction� Layer�

�Start� of� Received� TLP� on� the� “rxtlpu_data”�

�Start� of� Data� in� the� Received� TLP�

�End� of� TLP� on� the� “rxtlpu_data”�

�Type� of� Received� PM� DLLP�

�Valid� Signal� to� Sample� “rxpm_dllp_type”�

�Poisoned� TLP� received� indication�

�Unsupported� Request� Received� Indication�

�Malformed� TLP� Received� Indication�

�Bad� TLP� Received� Indication�

�Bad� DLLP� Received� Indication�

�Data� Link� Layer� Protocol� Error� Indication�

�REPLY_NUM� Rollover� Indication�

�Replay� Timer� Timeout� Indication�

�TX_USR� Interface�

�txtlpu_req�

�txtlpu_data[31:0]�

�txtlpu_st�

�txtlpu_end�

�txtlpu_nlfy�

�no_pcie_training�

�pkt_type�

�txpm_dllp_type�

�tx_pm�

�l_retrain_link�

�l_ext_sync�

�High�

�—�

�High�

�High�

�High�

�High�

�—�

�—�

�High�

�High�

�High�

�I�

�I�

�I�

�I�

�I�

�I�

�I�

�I�

�I�

�I�

�I�

�User� Interface� Request� to� Send� TLPs�

�TLP� Data� to� be� Transmitted� on� PCI� Express� Link�

�Start� of� TLP� Signal� that� Indicates� Start� of� New� TLP� on� the� txtlpu� _data�

�Bus�

�End� of� TLP� Signal� that� Indicates� End� of� TLP� on� the� txtlpu� _data� Bus�

�User� Interface� Request� to� Generate� a� Nulli?ed� TLP� This� Signal� is� to� be�

�Asserted� Along� With� End� of� TLP�

�No� LTSSM� Training� to� be� performed�

�Packet� type� for� credit� info�

�PM� packet� type� to� transmit�

�Send� PM� DLLP,� with� PM� data� in� “� tx_data� ”�

�Initiate� Link� Retraining�

�Extended� syn�

�Link� Control� bits� from� User� Interface�

�Bit� 0� –� Set� Hot_Reset� bit� in� TS1/TS2� Will� switch� the� Core� to� Reset� state� if�

�current� state� is� Recovery�

�loc_lnk_cntl[3:0]�

�High�

�I�

�Bit� 1� –� Set� Disable_Link� bit� in� TS1/TS2� Will� switch� the� Core� to� Disable� state�

�if� current� state� is� Recovery�

�Bit� 2� –� Set� Loopback� bit� in� TS1/TS2� Will� switch� the� Core� to� Tx_Loopback�

�state� if� current� state� is� Recovery�

�Bit� 3� –� Set� Disable_scramble� bit� in� TS1/TS2�

�l_go_config�

�txtlp_rdy�

�crdt_avail�

�High�

�High�

�—�

�I�

�O�

�O�

�Direct� the� Core� to� Switch� to� Con?guration� State�

�The� Data� Link� Layer� is� Ready� to� Accept� TLPs� from� Transaction� Layer�

�Credit� Available� for� the� Packet� Type�

�Note2:�

�1.� For� all� PCI� Express� Line� Interface� signals� (both� input� and� output)� refer� to� the� ORT42G5� and� ORT82G5� data� sheet� for� their� usage.�

�2.� External� Circuit� Interface:� rx_detect� signal� to� be� generated� by� an� external� circuit� whenever� the� start_rx_detect� signal� is� asserted.�

�Refer� to� the� Receiver� Detection� section� in� “PHY� Interface� for� the� PCI� Express� Architecture”.�

�3.� For� usage� of� loc_lnk_cntl� and� l_go_config� signals� refer� to� the� Link� Training� and� Status� State� Machine� section� of� the� PCI� Express�

�speci?cations.�

�14�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PCM18XH2

PROCESSOR MODULE MPLAB-ICE 2000

PCM18XN0

PROCESSOR MODULE FOR ICE2000

PDA-B-24-615-E-2B1-1-C

CIRCUIT BREAKER MAG 1P 15A

PFMF.260.2

PFMF PTC FUSE SMT 2.6A 1812

PFNF.200.2

PFNF PTC FUSE SMT 2A 1206

PFRY.375

PTC-FUSE RADIAL 72 VDC

PFSM.150.33.2

FUSE PTC 8A 15V FST-TRIP SMD

PFUF.150.2

FUSE PTC 3A 6V RESET SMD

相关代理商/技术参数

PCI-EXT+64U-

制造商:Twin Industries 功能描述:EXTENDER CARD, ACTIVE, BUS TYPE, 3.3 VOLTS TEST CARD,

PCI-G-EVB

功能描述:BOARD EVAL DISKONCHIP PCI-G RoHS:否 类别:编程器,开发系统 >> 过时/停产零件编号 系列:mDOC/mModule 标准包装:1 系列:- 传感器类型:CMOS 成像,彩色(RGB) 传感范围:WVGA 接口:I²C 灵敏度:60 fps 电源电压:5.7 V ~ 6.3 V 嵌入式:否 已供物品:成像器板 已用 IC / 零件:KAC-00401 相关产品:4H2099-ND - SENSOR IMAGE WVGA COLOR 48-PQFP4H2094-ND - SENSOR IMAGE WVGA MONO 48-PQFP

PCIH-10-6P

制造商:Amphenol Corporation 功能描述:CONN 26482 CIRC PIN 6 POS SLDR ST PNL MNT 6TERM - Bulk

PCIH-10-98P

制造商:Amphenol Corporation 功能描述:CONN 26482 CIRC PIN 6 POS SLDR ST PNL MNT 6TERM - Bulk

PCIH-12-10P

制造商:Amphenol Corporation 功能描述:CONN 26482 CIRC PIN 10 POS SLDR ST PNL MNT 10TERM - Bulk

PCIH-12-8P

制造商:Amphenol Corporation 功能描述:CONN 26482 CIRC PIN 8 POS SLDR ST PNL MNT 8TERM - Bulk

PCIH-14-12P

制造商:Amphenol Corporation 功能描述:CONN 26482 CIRC PIN 12 POS SLDR ST PNL MNT 12TERM - Bulk

PCIH-14-19P

制造商:Amphenol Corporation 功能描述:CONN 26482 CIRC PIN 19 POS SLDR ST PNL MNT 19TERM - Bulk